Характеристики кеша

- функція проекції блоків пам’яті на блоки кеша (в нас – пряма проекція);

- алгоритм заміни блоків кеша на блоки пам’яті(в нас – найпростіший, примусовий алгоритм);

- алгоритм виконання запису слова, як результату виконання дій в процесорі, до складної системи кеш-пам’ять (в нас застосовано спрощений алгоритм наскрізного запису).

Робота кеша

Детальний розгляд системи кеша залишено поза межами цієї статті. В даній статті пояснено роботу лише одного, спрощеного варіанту, відомого під назвою “кеш із прямою проекцією та наскрізним записом”. Звернемо увагу на те, що у поясненні фігурує термін "блок" з трьома можливими тлумаченнями:

- блок як інформаційна одиниця; він складається сусідніх за адресним принципом розташуванням слів без посилання на тип пам’яті;

- блок як множина комірок пам’яті даних або пам’яті інструкцій;

- блок як множина комірок робочої (внутрішньої) пам’яті кеша.

Розрізнення тлумачень не є важким, воно забезпечене контекстом пояснення.

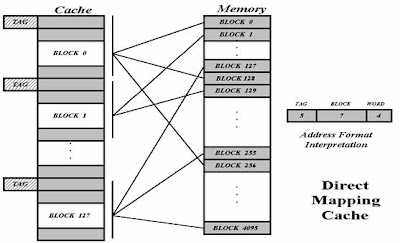

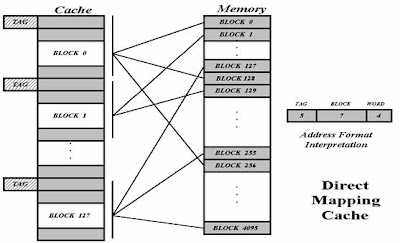

Кожний блок пам’яті, що складають у середньому з (16 –64) сусідніх з точки зору адресування слів, можна копіювати не до будь-якого, а тільки до наперед визначеного блоку робочої пам’яті кеша. В нас номер блоку кеша, що приймає участь у копіюванні, однозначно визначено за допомогою семи розрядів адреси процесора, які містить поле Block. Негайно зауважимо, що процесор “не розуміє” і не “сприймає” структурної інтерпретації адреси, що згенерував. Таку інтерпретацію адресі надає лише і тільки лише контролер кеша, коли “незаконно, без відома процесора” перехоплює цю адресу, що призначена пам’яті даних або пам’яті інструкцій.

Нехай адреса, яку генерує процесор при читанні вмістимого однієї комірки пам’яті (тобто, слова) до власного регістра, має довжину 16 бітів. В цьому випадку, контролер кеша за допомогою семи середніх розрядів адресного слова звертається до визначеного цими розрядами блоку власної пам’яті. Зрозуміло, що бінарний номер кеша є збіжним з бінарним наповненням поля Block адреси процесора. Шуканий в такий спосіб блок завжди присутній в робочій пам’яті кеша. При цьому кеш має складатись з 2(7)=128 блоків.

Але вмістиме винайденого блоку робочої пам’яті кеша може бути копією не одного, а одного з декількох дозволених на копіювання блоків пам’яті. Наприклад, в нас до нульового блоку кеша дозволено копіювати наступні блоки пам’яті: 0, 128, 256, 512 і т.д. Усього до кожного блоку кеша можна скопіювати один з 2(5)=32 блоків пам’яті. Зрозуміло, що інформаційна місткість пам’яті в 32 рази перевищує місткість кеша. Таке співвідношення місткостей є коректним згідно до означення парадоксу пам’яті. Доходимо висновку, що нас задовільнить лише однин з 32-х можливих варіантів копіювання. Питання лише в тому, чи є поточне наповнення визначеного блоку кеша відповідним запитанню процесора? Питання розв’язують за допомогою вмістимого старших п’яти бітів адреси процесора, які утворюють поле із назвою Tag.

Рис. Внутрішня структура кеша з прямою проекцією; в кеші внутрішню структуру кожного блоку як сукупності множини слів відбито, а пам’яті – приховано.

Якщо при вже визначеному номері блоку вмістиме блоку кеша є відповідним, тоді вмістиме полів tag з поля адреси процесора і з мітки блоку робочої пам’яті кеша співпадають, тоді у блок кеша в поточний момент містить потрібну копію. В цьому випадку фіксують ситуацію “влучення до кеша” (cache hit). Лишається за допомогою бітів правого поля формату адреси Word визначити шукане слово в межах винайденої в кеші копії блоку, яку щойно знайдено і перевірено на адекватність, та переслати це слово до входу процесора. Бачимо, що адресне запитання процесора на читання вмістимого комірки перехопив та задовільнив швидкий кеш, а повільна пам’ять не працювала.

Інша ситуація з назвою промах (cache miss) виникає при розбіжності вище зазначених двох тегів. Контролер кеша вимушений перетранслювати адресне запитання від процесора до повільної пам’яті та перейти (разом із процесором) до стану очікування результатів роботи пам’яті на читання. Аби зменшити кількість звернень до пам’яті навіть у цій ситуації, читають не одне, вказане адресою процесора слово, а цілий інформаційний блок (з 16-64 сусідніх слов), який, безперечно, має містити шукане процесором слово пам’яті. Тут спрацьовує принцип локалізації адресних звертань процесора – “наступне слово, що знадобиться процесору, скорше від усього, буде мати і наступну адресу”.

Блок надсилають до кеша, де його копіюють до блоку робочої пам’яті із вже відомим номером, і, водночас, потрібне слово з цього блоку, подають до інформаційного входу процесора. Зрозуміло, що при копіюванні інформаційного блоку з пам’яті до блоку робочої пам’яті кеша перевизначають вмістиме відповідного тегового поля.

Під час запису (пересилання слова з регістру процесора до комірки пам’яті) робота контролера кеша виконується так. Спочатку визначають присутність або відсутність копії блоку, який містить старе значення, відповідного до наданої процесором адреси. У разі влучення до кеша запис виконують як до блоку кеша, так і до блоку пам’яті, інакше тільки до блоку пам’яті Але в обидвох випадках запис виконують повільно через обов’язкову участь у ньому повільної пам’яті даних. Зазначимо, що пояснений алгоритм запису реалізує так званий кеш із наскрізним записом.

Більш складні, але ефективні алгоритми запису, ми не розглядаємо і пропонуємо з цього питання звернутися до інших джерел.

![]()

![]()

![]()