Число вхідних каналів логічного аналізатора в більшому або меншому ступені визначається можливостями приладу. Наприклад, якщо застосовується для аналізу 8-розрядної логічний аналізатор мікропроцесорної системи з 16-розрядною адресною шиною, 8-розрядною шиною даних і п'ятьма або шістьма лініями керування, то мінімальне число необхідних вхідних каналів аналізатора ідеально дорівнює 30. Для повного аналізу 16-розрядної мікропроцесорної системи аналогічно буде потрібно логічний аналізатор приблизно з 46 вхідними каналами. Його повний вхідний опір подібно осцилографам звичайно дорівнює 1 МОм, а номінал паралельно включеної ємності 10-15 пФ.

Іншим чинником, що визначає характеристики логічного аналізатора, є гнучкість запуску. На відміну від осцилографа, що звичайно запускається при першому перетинанні вхідним сигналом заздалегідь заданого граничного значення, логічний аналізатор повинний мати декілька додаткових режимів запуску. Найважливішими з них є такі:

1. Запуск при появі заданого слова даних, тобто аналізатор запускається, коли вхідні сигнали формують окрему (часткову) комбінацію даних;

2. Передзапуск/післязапуск, що використовуються для запам'ятовування, а якщо необхідно, то й для індикації вхідних даних, що прийшли до поступленого слова і після нього;

3. Запуск, коли виникає визначена різниця між очікуваними сигналами й отриманими вхідними даними;

4. Запам'ятовування й індикація даних, прийнятих за визначений часовий інтервал (звичайно визначається числом циклів тактового генератора) після поступаючого слова;

5. Запам'ятовування й індикація даних, прийнятих після визначеного числа появ поступаючого слова;

6. Порівняння подій по фактичним даним з очікуваними подіями і запуск тільки в тому випадку, якщо вони не збігаються.

Важливими чинниками, що визначають характеристики аналізатора, є обсяг пам'яті і швидкість зчитування. Пам'ять часто виконується секційовано і складається з декількох сегментів, необхідних для запам'ятовування різноманітних типів даних (еталонних, фактично запам’ятованих і інформації про сигнали, що швидко змінюються). Користувач сам визначає, який сегмент пам'яті варто використовувати для виконання визначених функцій. Типовий обсяг пам'яті одного сегмента складає від 64 слів до 2К слів.

Тимчасове вікно, тобто проміжок часу, протягом якого можуть спостерігатися сигнальні дані, безпосередньо визначається загальним обсягом пам'яті логічного аналізатора. У ситуаціях, коли немає необхідності у використанні усіх вхідних сигнальних каналів логічного аналізатора, сегменти пам'яті об'єднуються в послідовні ланки таким чином, щоб менша кількість вхідних сигналів можна було спостерігати в більш тривалому тимчасовому вікні.

Часто в аналізатор вбудовують цифровий генератор слів, що забезпечує стимулюючі впливи на досліджувану мікропроцесорну систему. У цьому випадку аналізатор може застосовуватися для спостереження за тим, що відбувається в системі під дією цих стимулюючих сигналів.

Більш складні логічні аналізатори мають енергетично-незалежну пам'ять (ЕНПЗП, КМОП, ОЗП з батарейним живленням і т.п.) для зчитування, запису вхідних даних, розміщення в ній інформації користувача або еталонної інформації, а також для її порівняння з інформацією, що надходить. У ряді випадків, якщо потрібно великий обсяг пам'яті даних, використовується пам'ять на гнучких-дисках. Багато логічних аналізаторів припускають проведення прямих порівнянь між новими поступаючими й еталонними даними. Іноді логічні аналізатори оснащуються двома і навіть трьома тактовими системами, що дозволяють здійснювати ввід даних, наприклад, із мультиплексованих мікропроцесорних систем.

Розглянуті в цьому параграфі особливості аналізаторів не є заданими раз і назавжди. Вони в більшому ступені залежать від вимог користувача. Оскільки самі по собі логічні аналізатори є приладами, спроектованими на основі мікропроцесорів, то їхні характеристики іноді можуть змінюватися вже на стадії виготовлення за рахунок модифікації програмного забезпечення.

2 листопада 2007 р.

Особливості логічних аналізаторів

Логічні аналізатори

Логічний аналізатор є однією з модифікацій цифрового запам’ятовуючого осцилографа і виконує необхідні функції представлення інформації в не реальному часі Замість максимум чотирьох сигнальних входів як в осцилографа, аналізатор має 8, 16, 32, 48 і більш сигнальних входів у залежності від конструкції і, звичайно, вартості. Слід зазначити, проте, що на цьому аналогія між цифровим запам’ятовуючим осцилографом і логічним аналізатором закінчується. Осцилограф є апаратним випробовувальним приладом, побудованим для спеціальних цілей відображення сигналів у часовій області, тоді як логічний аналізатор - це прилад із мікропроцесорним керуванням і програмним забезпеченням, що володіє значно більшими можливостями, ніж просто індикація в часовій області запам’ятованих сигналів. Логічний аналізатор може маніпулювати запам’ятованими сигналами, перетворювати їх в алфавітно-цифрові дані для індикації і навіть дозволяє спостерігати по кроках за роботою програмного забезпечення досліджуваної мікропроцесорної системи.

Оскільки логічний аналізатор є мікропроцесорною системою з власними правилами побудови, роздивимося прилад «зсередини».

Більшість логічних аналізаторів, побудованих на основі мікропроцесорів, є універсальними не тільки з погляду виконуваних ними функцій, але й у тому відношенні, що вони можуть бути використані для виміру сигналів будь-яких типів. Підключення універсального мікропроцесорних системлогічного аналізатора до окремої мікропроцесорної системи провадиться через спеціалізований інтерфейсний модуль, що синхронізує аналізатор із мікропроцесорною системою. Для передачі даних із мікропроцесорної системи в аналізатор використовуються необхідні електричні і механічні з'єднання.

Таким чином, один інтерфейсний модуль може застосовуватися для з'єднання логічного аналізатора з будь-якою системою, побудованою на основі мікропроцесора Z-80, тоді як інший модуль використовується для приєднання аналізатора до будь-якої системи, основаної на мікропроцесорі 8085, і т.д.

Різні виробники устаткування дають різні назви інтерфейсним модулям, наприклад модулі персоніфікації або «препроцесори», але найбільш часто їх називають подами (Pod - окремий відсік). Звичайно модулі персоніфікації є окремими приладами і зв'язуються з логічним аналізатором і мікропроцесорною системою за допомогою гнучких кабелів і змінних роз’ємів. Проте в ряді випадків, особливо в спеціалізованих логічних аналізаторах, функції подів реалізуються на друкарських платах, вмонтованих в аналізатор.

При з'єднанні з мікропроцесорною системою через модуль персоніфікації універсальний аналізатор стає комбінованим логічним аналізатором.

Деякі логічні аналізатори випускаються як і випробовувальна апаратура, спеціалізована під мікропроцесор, але це, очевидно, обмежує область застосування тільки одним типом мікропроцесорних систем, і тому такі аналізатори дуже специфічні і мають високу вартість.

4 жовтня 2007 р.

Хаб

Хаб (hub, repeater, повторювач, концентратор, розгалужувач) - пристрій, що служить для "розгалуження" сигналу в сегменті мережі. Сигнал, отриманий хабом на одному порті, посилюється і передається на всі порти пристрою. Портів може бути мінімум 2, тоді це називається "повторювач" (repeater), найчастіше такі 2х-портові хаби застосовувалися в коаксіальних мережах і служили для "подовження" мережі. При використанні хабів можливі колізії. Хаби вносять певну затримку до розповсюдження сигналу. Хаби, як і мережеві карти, є пристроями 1-го рівня, тобто працюють з мережею на рівні сигналів.

3 жовтня 2007 р.

Автокад (Autocad)

Автокад (Autocad) — система автоматизованого проектування і креслення компанії Autodesk. Сімейство продуктів Автокад є одним з найбільш поширених САПР у світі. Виробник Автокад компанія Autodesk займається розробкою САПР Автокад понад 20 років. За цей час були створені тисячі доповнень і спеціалізовані рішення від сторонніх фірм і самої компанії Autodesk. На даний момент в світі налічується близько 6 мільйонів користувачів Автокад.

В перших редакціях, Автокад використовував примітивні об'єкти (лінії, круги, дуги, текст). Від середини-1990-х років, Автокад підтримує об'єкти через його C++ програмний інтерфейс. Сучасний Автокад включає повний набір інструментів для моделювання та 3D графіки. Автокад підтримує ряд інтерфейсів: AutoLISP, Visual LISP, VBA, .NET та ObjectARX.

Автокад останніми роками забезпечив підтримку DWF, цей формат розвинувся і просувається Autodesk для зберігання даних САПР.Автокад LT (Autocad LT)

Автокад LT (Autocad LT) є "врізаною" версією Автокад. Автокад LT коштує менше (близько $900 проти близько $4,000 для повного Автокад). Автокад LT версія також доступна для купівлі в магазинах з продажу комп'ютерів і супутніх товарів, на відміну від Автокад, який продається виключно офіційним дилером Autodesk.

27 вересня 2007 р.

Особливості використання аналогових та цифрових осцилографів

Властивості цифрових осцилографів і аналізаторів

- можливість індикації стану досліджуваних сигналів до момента синхронізації (момента виникнення збою);

- вбудовані пастки для поодиноких імпульсів досліджуваних сигналів;

- вбудовані пастки для комбінацій вхідних сигналів (аналізатори);

- зв'язок з управляючою ЕОМ з допомогою стандартних інтерфейсів (IEEE 488, VXI).

Типи осцилографів

- аналогові осцилографи ;

- цифрові осцилографи .

В даний час аналогові осцилографи вже не випускаються.

Аналогові осцилографи призначені для дослідження аналогових сигналів.

Параметри аналогових осцилографів

- смуга пропускання (0 Гц ... 1 ГГц). При смузі пропускання в 1 ГГц структура осцилографів дуже складна.

- довжина фронту: переднього tп.ф. и заднього tз.ф. Оскільки вони близькі, то часто говорять про тривалість фронту tф і вважають, що вона характеризує і передній і задній фронти сигналу.

Відношення смуги пропускання і довжини фронту повинно задовільняти наступній нерівності: ![]()

Для вибору аналогового осцилографа використовують наступне правило:

![]()

де F=1/T, T – період сигналу.

![]()

f = 100 МГц, Tосц=1/f, tосц=0.1Тосц

Недоліки аналогових осцилографів

- можна дивитись лише періодичні сигнали;

- не можна дивитись передісторію сигналів;

- немає процесора, каналів зв’язку, тому неможливе комлексування.

Цифрові осцилографи

Основні властивості цифрових осцилографів

- можливість індикації стану досліджуваних сигналів до момента синхронізації (момента виникнення збою);

- вбудовані пастки для поодиноких імпульсів досліджуваних сигналів;

- зв'язок з управляючою ЕОМ з допомогою стандартних інтерфейсів (IEEE 488, VXI).

Цифрові осцилографи мають вбудовані в собі мікропроцесор, оперативний запам’ятовуючий пристрій для запам’ятовування сигналів. На цифровому осцилографі можна дивитись будь-які сигнали, як періодичні так і неперіодичні.

Також можна дивитись передісторію (до моменту синхронізації) оскільки в цифрових осцилографах використовується запис в пам'ять.

Цифрові осцилографи мають більш складну структуру в порівнянні з аналоговими осцилографами. Зараз цифровий осцилограф – це персональний комп'ютер з платою аналогово-цифрового перетворювача.

Найкращі цифрові осцилографи випускає фірма HP. Найбільш розповсюджена серія цифрових осцилографів є HP 54XXX:

Таблиця Цифрові осцилографи

| Параметр | наймолодший представник сімейства | середній представник сімейства | найстарший представник сімейства |

| смуга пропускання | 60 МГц | 500 МГц | 12000 МГц |

| кількість сигналів, які одночасно можна досліджувати | 1 | 2 | 4 |

| об'єм пам'яті на канал | 1к х 8 розрядів | 32к х 8 розрядів | 256к х 12 розрядів |

Цифровий осцилограф має вбудований в собі мультиметр.

Інформація від осцилографа зберігається на флопі-диску.

Також до осцилографа можна під'єднати принтер. Цифровий осцилограф має в собі вбудовані інтерфейси RS232, HPIB.

Ціна цифрового осцилографа може досягати $20 000.

Мітки: Осцилографи, Цифрові осцилографи

25 вересня 2007 р.

Закон Амдала

Умови Закону Амдала

1. Продуктивність комп'ютерних систем, яка складається із зв'язаних між собою пристроїв в загальному випадку визначається як найбільш непродуктивна.

2. Нехай комп'ютерна система створена із S однакових простих універсальних пристроїв. Нехай припустимо, що при виконанні паралельної частини алгоритму всі S пристроїв завантажені повністю. Тоді максимально можливе прискорення

Припустимо, що з якихось причин n операцій виконано послідовно, N - загальна кількість операцій.

3. Нехай система створена із простих однакових універсальних пристроїв, при будь-якому режимі роботи її прискорення не може перебільшувати зворотньої величини частки послідовних обчислень.

Якщо послідовно виконуються m операцій, то число ярусів будь-якої паралельної форми алгоритму, не може бути менше n.

В дослідженнях по закону Амдала не конкретизується зміст операцій. В загальному випадку вони можуть бути як елементарними так і дуже складними, і являють собою алгоритм розв’язку достатньо складних задач.

Формулювання закону Амдала не враховує тимчасових витрат на забезпечення обміну інформацією між обчислювальними вузлами.

Наслідок із закону Амдала: для того, щоб прискорити виконання програми в q разів необхідно прискорити не менше, ніж в q разів не менше, ніж (1-1/q) -у частину програми.

Комп'ютерних систем із великою кількісттю процесорів має бути завантажено достатньо богато, в іншому випадку немає змісту їх створювати. Дослідження закону Амдала показали, що в паралельних системах доля послідовних операцій має бути порядку десятих і сотих відсотка.

Закон Амдала деякою мірою допомагає відчути складність паралельного програмування: наприклад, для прискорення виконання програми в 100 разів, необхідно, щоб 99,99% операцій в програмі можливо було б виконувати з 100-кратним розпаралеленням.

Мітки: Закон Амдала

Характеристики і робота кеша

Характеристики кеша

- функція проекції блоків пам’яті на блоки кеша (в нас – пряма проекція);

- алгоритм заміни блоків кеша на блоки пам’яті(в нас – найпростіший, примусовий алгоритм);

- алгоритм виконання запису слова, як результату виконання дій в процесорі, до складної системи кеш-пам’ять (в нас застосовано спрощений алгоритм наскрізного запису).

Робота кеша

Детальний розгляд системи кеша залишено поза межами цієї статті. В даній статті пояснено роботу лише одного, спрощеного варіанту, відомого під назвою “кеш із прямою проекцією та наскрізним записом”. Звернемо увагу на те, що у поясненні фігурує термін "блок" з трьома можливими тлумаченнями:

- блок як інформаційна одиниця; він складається сусідніх за адресним принципом розташуванням слів без посилання на тип пам’яті;

- блок як множина комірок пам’яті даних або пам’яті інструкцій;

- блок як множина комірок робочої (внутрішньої) пам’яті кеша.

Розрізнення тлумачень не є важким, воно забезпечене контекстом пояснення.

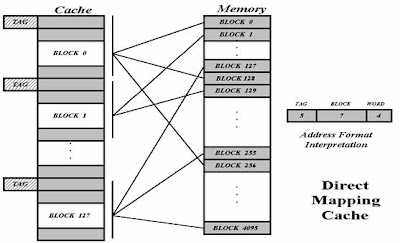

Кожний блок пам’яті, що складають у середньому з (16 –64) сусідніх з точки зору адресування слів, можна копіювати не до будь-якого, а тільки до наперед визначеного блоку робочої пам’яті кеша. В нас номер блоку кеша, що приймає участь у копіюванні, однозначно визначено за допомогою семи розрядів адреси процесора, які містить поле Block. Негайно зауважимо, що процесор “не розуміє” і не “сприймає” структурної інтерпретації адреси, що згенерував. Таку інтерпретацію адресі надає лише і тільки лише контролер кеша, коли “незаконно, без відома процесора” перехоплює цю адресу, що призначена пам’яті даних або пам’яті інструкцій.

Нехай адреса, яку генерує процесор при читанні вмістимого однієї комірки пам’яті (тобто, слова) до власного регістра, має довжину 16 бітів. В цьому випадку, контролер кеша за допомогою семи середніх розрядів адресного слова звертається до визначеного цими розрядами блоку власної пам’яті. Зрозуміло, що бінарний номер кеша є збіжним з бінарним наповненням поля Block адреси процесора. Шуканий в такий спосіб блок завжди присутній в робочій пам’яті кеша. При цьому кеш має складатись з 2(7)=128 блоків.

Але вмістиме винайденого блоку робочої пам’яті кеша може бути копією не одного, а одного з декількох дозволених на копіювання блоків пам’яті. Наприклад, в нас до нульового блоку кеша дозволено копіювати наступні блоки пам’яті: 0, 128, 256, 512 і т.д. Усього до кожного блоку кеша можна скопіювати один з 2(5)=32 блоків пам’яті. Зрозуміло, що інформаційна місткість пам’яті в 32 рази перевищує місткість кеша. Таке співвідношення місткостей є коректним згідно до означення парадоксу пам’яті. Доходимо висновку, що нас задовільнить лише однин з 32-х можливих варіантів копіювання. Питання лише в тому, чи є поточне наповнення визначеного блоку кеша відповідним запитанню процесора? Питання розв’язують за допомогою вмістимого старших п’яти бітів адреси процесора, які утворюють поле із назвою Tag.

Рис. Внутрішня структура кеша з прямою проекцією; в кеші внутрішню структуру кожного блоку як сукупності множини слів відбито, а пам’яті – приховано.

Якщо при вже визначеному номері блоку вмістиме блоку кеша є відповідним, тоді вмістиме полів tag з поля адреси процесора і з мітки блоку робочої пам’яті кеша співпадають, тоді у блок кеша в поточний момент містить потрібну копію. В цьому випадку фіксують ситуацію “влучення до кеша” (cache hit). Лишається за допомогою бітів правого поля формату адреси Word визначити шукане слово в межах винайденої в кеші копії блоку, яку щойно знайдено і перевірено на адекватність, та переслати це слово до входу процесора. Бачимо, що адресне запитання процесора на читання вмістимого комірки перехопив та задовільнив швидкий кеш, а повільна пам’ять не працювала.

Інша ситуація з назвою промах (cache miss) виникає при розбіжності вище зазначених двох тегів. Контролер кеша вимушений перетранслювати адресне запитання від процесора до повільної пам’яті та перейти (разом із процесором) до стану очікування результатів роботи пам’яті на читання. Аби зменшити кількість звернень до пам’яті навіть у цій ситуації, читають не одне, вказане адресою процесора слово, а цілий інформаційний блок (з 16-64 сусідніх слов), який, безперечно, має містити шукане процесором слово пам’яті. Тут спрацьовує принцип локалізації адресних звертань процесора – “наступне слово, що знадобиться процесору, скорше від усього, буде мати і наступну адресу”.

Блок надсилають до кеша, де його копіюють до блоку робочої пам’яті із вже відомим номером, і, водночас, потрібне слово з цього блоку, подають до інформаційного входу процесора. Зрозуміло, що при копіюванні інформаційного блоку з пам’яті до блоку робочої пам’яті кеша перевизначають вмістиме відповідного тегового поля.

Під час запису (пересилання слова з регістру процесора до комірки пам’яті) робота контролера кеша виконується так. Спочатку визначають присутність або відсутність копії блоку, який містить старе значення, відповідного до наданої процесором адреси. У разі влучення до кеша запис виконують як до блоку кеша, так і до блоку пам’яті, інакше тільки до блоку пам’яті Але в обидвох випадках запис виконують повільно через обов’язкову участь у ньому повільної пам’яті даних. Зазначимо, що пояснений алгоритм запису реалізує так званий кеш із наскрізним записом.

Більш складні, але ефективні алгоритми запису, ми не розглядаємо і пропонуємо з цього питання звернутися до інших джерел.

Мітки: Кеш, пам'ять, Робота кеша, Характеристики кеша

24 вересня 2007 р.

Швидкість RSA. Гібридні криптосистеми

Найбільша швидкіcть реалізації RSA в 1000 разів повільніша, ніж DES. В 1989 році Найбільші швидкоcті VKSI- реалізації дорівнювали приблизно 64 Kб/c. Зараз швидкість ~1 Мб/с. (для порівняння швидкість DES(ГОСТ) – від 10 до 100 Мб/с). Числа можуть змінюватись, але швидкість RSA ніколи не досягне швидкості симетричних алгоритмів. Ось чому на практиці більшість систем використовує RSA виключно для обміну DES’івськими ключами, а потім шифрують всі інші DES’ом. Такий підхід називається гібридними криптосистемами. Криптографія з відкритим ключем ідеальна для шифрування й розподілу ключів, автентифікації та ін. Симетрична криптографія ідеальна для шифрування файлів й каналів зв’язку.

Алгоритми розкладу на множники (факторизація)

Факторизація - розклад чисел на прості множники.

Можна виділити два основних типи - спеціалізовані й універсальні алгоритми розкладу на множники.

Один з найбільш потужних спеціалізованих алгоритмів розкладу на множники - метод еліптичних кривих (режим виправлення помилок), що був винайдений в 1985 році Х.Ленстром молодшим. Час виконання цього методу залежить від розміру головних множників n, і відповідно алгоритм має тенденцію знаходити спочатку маленькі множники. До розвитку RSA системи шифрування, найкращим універсальним алгоритмом розкладу на множники був алгоритм ланцюгового поділу. Цей алгоритм розкладу на множники був оснований на ідеї відносного використання основи множника штрихів та добутку, пов’язаного з набором лінійних рівнянь, його рішення в кінцевому рахунку вело до факторизації. Та ж ідея лежить в основі найкращих універсальних алгоритмів розкладу на множники, що використовуються сьогодні: квадратична сітка (QS) та сітка поля цифр (NFS). Обидва ці алгоритми можуть бути легко паралелізовані, щоб дозволити розклад на множники на розпаралелених мережах АРМ. Квадратична сітка (решето) була розроблена Карлом Померансом 1984р. В 1994 році вона була використана групою дослідників на чолі з А.Ленстром до 129-розрядного множника 429- розрядного добутку модуля RSA, що був викладений Мартином Гарднером у 1977р. Факторизація була виконана через 8 місяців приблизно на 1600 комп’ютерах у всьому світі.

Експерименти довели, що NFS є дійсно добрим алгоритмом для розкладу на множники чисел, що мають принаймні 120 десяткових цифр (400 бітів).

Електронний підпис на основі алгоритму RSA

Наприкінці звичайного листа або документа виконавець чи відповідальна особа зазвичай ставить свій підпис. Подібна дія зазвичай переслідує дві мети. По-перше, одержувач має можливість переконатися в автентичності листа, звіривши підпис з наявним у нього зразком. По-друге, особистий підпис є юридичним гарантом авторства документа. Із поширенням у сучасному світі електронних форм документів (у тому числі і конфіденційних) і засобів їхньої обробки особливо актуальною стала проблема встановлення дійсності та авторства непаперової документації. За всіх переваг сучасних систем шифрування вони не дозволяють забезпечити автентифікацію даних. Тому засоби автентифікації повинні використовуватися в комплексі з криптографічними алгоритмами.

Алгоритм RSA є найбільш простим і розповсюдженим інструментом електронного підпису.

Мітки: Автентифікація, Алгоритм RSA, Електронний підпис, Криптографія, RSA